# **MIPS 4K/5KTM Lead Vehicle Datasheet**

Document Number: MD00001 Revision 01.10 July 27, 2001

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 1999-2000 MIPS Technologies Inc. All right reserved.

Copyright © 1999-2000 MIPS Technologies, Inc. All rights reserved.

Unpublished rights reserved under the Copyright Laws of the United States of America.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying, or use of this information (in whole or in part) which is not expressly permitted in writing by MIPS Technologies or a contractually-authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

MIPS Technologies or any contractually-authorized third party reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error of omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Any license under patent rights or any other intellectual property rights owned by MIPS Technologies or third parties shall be conveyed by MIPS Technologies or any contractually-authorized third party in a separate license agreement between the parties.

The information contained in this document shall not be exported or transferred for the purpose of reexporting in violation of any U.S. or non-U.S. regulation, treaty, Executive Order, law, statute, amendment or supplement thereto.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or any contractually-authorized third party.

MIPS<sup>®</sup>, R3000<sup>®</sup>, R4000<sup>®</sup>, R5000<sup>®</sup> and R10000<sup>®</sup> are among the registered trademarks of MIPS Technologies, Inc. in the United States and certain other countries, and MIPS16<sup>TM</sup>, MIPS16e<sup>TM</sup>, MIPS32<sup>TM</sup>, MIPS64<sup>TM</sup>, MIPS-3D<sup>TM</sup>, MIPS-based<sup>TM</sup>, MIPS II<sup>TM</sup>, MIPS III<sup>TM</sup>, MIPS III<sup>TM</sup>, MIPS IV<sup>TM</sup>, MIPS V<sup>TM</sup>, MDMX<sup>TM</sup>, SmartMIPS<sup>TM</sup>, 4K<sup>TM</sup>, 4Kc<sup>TM</sup>, 4Km<sup>TM</sup>, 4Ke<sup>TM</sup>, 4KEc<sup>TM</sup>, 4KEp<sup>TM</sup>, 4KEp<sup>TM</sup>, 4KSc<sup>TM</sup>, 5K<sup>TM</sup>, 5Kc<sup>TM</sup>, 5Kf<sup>TM</sup>, 20K<sup>TM</sup>, 20Kc<sup>TM</sup>, R20K<sup>TM</sup>, R4300<sup>TM</sup>, ATLAS<sup>TM</sup>, CoreLV<sup>TM</sup>, EC<sup>TM</sup>, JALGO<sup>TM</sup>, MALTA<sup>TM</sup>, MGB<sup>TM</sup>, SEAD<sup>TM</sup>, SEAD-2<sup>TM</sup>, SOC-it<sup>TM</sup> and YAMON<sup>TM</sup> are among the trademarks of MIPS Technologies, Inc.

All other trademarks referred to herein are the property of their respective owners.

## Table of Contents

| 1 Introduction                                                           | 4   |

|--------------------------------------------------------------------------|-----|

| 1.1 Main Features                                                        | 4   |

| 1.2 Dual Bus Modes                                                       | 6   |

| 2 Pin Description                                                        |     |

| 2.1 Shared Pins with Identical Function in Both SysAD64 and Bond-out Mod | le8 |

| 2.2 Functional Pin Specification in SysAD64 Mode                         |     |

| 2.3 Functional Pin Specification in Core Bond-out Mode                   |     |

| 2.3.1 SI_MergeMode, SI_SimpleBE changes                                  |     |

| 2.3.2 Unavailable Core Ports in Bond-out Mode                            |     |

| 3 Clocking and Reset                                                     |     |

| 3.1 SysAD64 with PLL Enabled                                             |     |

| 3.1.1 Reset                                                              |     |

| 3.2 Core Bond-out with PLL Bypassed                                      |     |

| 3.2.1 Reset                                                              |     |

| 4 Bus Protocols                                                          |     |

| 4.1 SysAD64 Bus Mode                                                     |     |

| 4.1.1 SysAD Interface Signals                                            |     |

| 4.1.2 SysAD Bus Controller Configuration Signals                         |     |

| 4.1.3 Commands and Data Identifiers                                      |     |

| 4.1.4 SysCmd Bits                                                        |     |

| 4.1.5 SysCmd encodings for the address cycles                            |     |

| 4.1.6 SysCmd Encodings for the Read Response Data Cycles                 |     |

| 4.1.7 SysCmd Encodings for the Write Data Cycles                         |     |

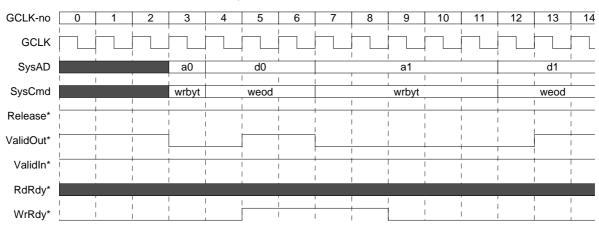

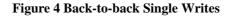

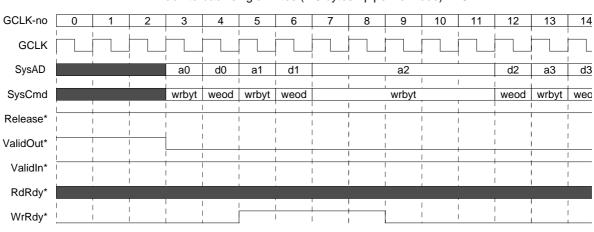

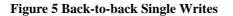

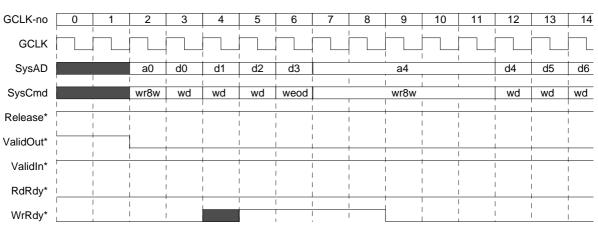

| 4.1.8 Basic SysAD Access Patterns                                        |     |

| 4.1.9 Read Transactions                                                  |     |

| 4.1.10 Write Transactions                                                |     |

| 4.1.11 Low Order SysAD Address Behavior                                  |     |

| 4.2 Core Bond-out Mode                                                   |     |

| 4.3 General PCB Design Rules                                             |     |

| AC, DC Specifications                                                    |     |

| 5.1 AC/DC Specifications for Pins with Identical Function in Both Modes  |     |

| 5.2 AC/DC Specifications for Multiplexed Pins in SysAD64 Mode            |     |

| 5.3 AC/DC Specifications for Multiplexed Pins in Core Bond-out Mode      |     |

| 5.4 Power Supplies                                                       |     |

| 6 Implementation Specific Data                                           |     |

| 6.1 Identification                                                       |     |

| 6.2 Cache Size                                                           |     |

| 6.3 Supply Voltages                                                      |     |

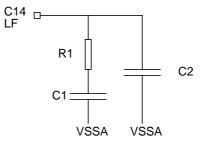

| 6.4 PLL Connections                                                      |     |

| 6.5 PLL Loop Filter Types, Component Values and Frequency Range          |     |

| 7 Package and Pinout                                                     |     |

| 7.1 PLL Connections                                                      |     |

| 7.1.1 General PCB Design Rules for PLL Connections                       |     |

| 7.1.1 Ochetai i CD Design Rules for i LL Connections                     |     |

| endices                                                                  | 48  |

| A Revision History                                                       |     |

|                                                                          |     |

## **1** Introduction

This document contains the user level documentation for the MIPS 4K and 5K lead vehicle chips. The lead vehicle (called "LV" throughout the rest of this document) is a testchip specified by MIPS which all core licensees must produce in order to allow testing of silicon functionality.

This document does not describe the internal details of the 4K & 5K microprocessor cores, it only concentrates on the issues relevant for using the LV chips in a hardware design process, e.g. pinout, bus protocols, timing etc.

In most aspects relevant for this document, the LV chips for 4K & 5K cores are identical, as the package, pinout and bus protocol employed is the same. In situations where a difference exists, it will be clearly noted.

For detailed information on silicon specific data for a particular LV, a "Specification Update" document is issued for each. These documents are the definitive source of information regarding a specific LV implementation, and both this general datasheet as well as the specification update must be read in order to obtain the complete set of relevant information.

## 1.1 Main Features

Most of the features in the 4K & 5K LVs are identical:

- LV is a fully equipped chip which is usable for both evaluation purposes and real designs

- Supports industry standard SysAD64 bus protocol

- Built-in PLL to generate core clock from bus clock

- Supports core bond-out mode for SOC development applications

- BGA package with 388 balls

- Separate I/O and core supplies allows real-time power measurements

- All I/Os are 3.3V with TTL thresholds

The following tables describe the areas where there is a difference:

| Feature                      | 4K LV (4Kc/m)                                   | 4K LV (4Kp)        | 4KE, 4KS LV<br>(4KEc/m, 4KSc)                   | 4KE LV (4KEp)      |

|------------------------------|-------------------------------------------------|--------------------|-------------------------------------------------|--------------------|

| Instruction set architecture | MIPS32                                          | MIPS32             | MIPS32                                          | MIPS32             |

| FPU included                 | No                                              | No                 | No                                              | No                 |

| Cache implementation         | Write-Through                                   | Write-Through      | Write-Back                                      | Write-Back         |

| Cache set size               | 4 kByte                                         | 4 kByte            | 16 kByte                                        | 16 kByte           |

| Associativity (I/D)          | 4I, 4D                                          | 4I, 4D             | 4I, 4D                                          | 4I, 4D             |

| Total cache size (I/D)       | 16 kByte, 16 kByte                              | 16 kByte, 16 kByte | 64 kByte, 64kByte                               | 64 kByte, 64 kByte |

|                              | SW configurable:                                |                    | SW configurable:                                |                    |

| MMU                          | TLB, 16 dual entries<br>OR<br>Fixed mapping MMU | Fixed mapping MMU  | TLB, 16 dual entries<br>OR<br>Fixed mapping MMU | Fixed mapping MMU  |

| EJTAG                        | Version 2.5                                     | Version 2.5        | Version 2.6                                     | Version 2.6        |

| Table 1 Feature Differences (4K class LVs) | Table 1 | Feature | Differences | (4K | class | LVs) |

|--------------------------------------------|---------|---------|-------------|-----|-------|------|

|--------------------------------------------|---------|---------|-------------|-----|-------|------|

| Feature                         | 4K LV (4Kc/m)                     | 4K LV (4Kp)                       | 4KE, 4KS LV<br>(4KEc/m, 4KSc) | 4KE LV (4KEp)               |

|---------------------------------|-----------------------------------|-----------------------------------|-------------------------------|-----------------------------|

| PDtrace                         | Not available                     | Not available                     | Yes                           | Not available               |

| PLL clock multipliers supported | 2x, 3x, 4x<br>2x (RTL ver <= 3.2) | 2x, 3x, 4x<br>2x (RTL ver <= 3.2) | 2x, 3x, 4x                    | 2x, 3x, 4x                  |

| Maximum core clock speed        | Implementation<br>dependent       | Implementation<br>dependent       | Implementation<br>dependent   | Implementation<br>dependent |

Table 1 Feature Differences (4K class LVs)

#### Table 2 Feature Differences (5K class LVs)

| Feature                         | 5K LV (5Kc/m)                                   | 5K LV (5Kf)                                     |

|---------------------------------|-------------------------------------------------|-------------------------------------------------|

| Instruction set architecture    | MIPS64                                          | MIPS64                                          |

| FPU included                    | No                                              | Yes                                             |

| Cache implementation            | Write-Back                                      | Write-Back                                      |

| Cache set size                  | 16 kByte                                        | 16 kByte                                        |

| Associativity (I/D)             | 4I, 4D                                          | 4I, 4D                                          |

| Total cache size (I/D)          | 64 kByte, 64 kByte                              | 64 kByte, 64 kByte                              |

|                                 | SW configurable:                                | SW configurable:                                |

| MMU                             | TLB, 32 dual entries<br>OR<br>Fixed mapping MMU | TLB, 32 dual entries<br>OR<br>Fixed mapping MMU |

|                                 | Version 2.5                                     |                                                 |

| EJTAG                           | EJTAG version 2.6 in<br>RTL ver. 2.2 or later   | Version 2.6                                     |

| PDtrace                         | Not available                                   | Not available                                   |

| PLL clock multipliers supported | 2x, 3x, 4x                                      | 2x, 3x, 4x                                      |

| Maximum core clock speed        | Implementation<br>dependent                     | Implementation<br>dependent                     |

Note that with regards to MMU functionality, there are two types of 4K and 4KE LVs. The first one implements the functionality of both the 4Kc and 4Km (4KEc, 4KEm) products (different MMUs). Which one to use is software configurable. This allows customers to get "two cores in one LV", and The second type of 4K LV implements the 4Kp (4KEp) product, which only contains the fixed mapping MMU and the slow multiplier.

The clock multiplier support in 4K LVs is depending on the RTL version they are built on. Versions built using RTL version 3.2 or earlier supports only the 2x multiplier. Newer versions (RTL version 3.3 and later) support the full range of clock multipliers (2x, 3x, 4x). The RTL version for a specific LV is documented in the "Specification Update" document for that particular silicon. For 4KE and 4KS LV's, all versions support the full set of clock multipliers.

For 5K LVs, all implement both the TLB style MMU and the fixed mapping MMU functionality, again software controllable.

For the 4KE, 4KS and 5K LVs, the indicated cache sizes are the maximum sizes supported. In some cases, implementations might implement smaller caches due to limitations in the available memory blocks. The actual implementation specific details are described in a later chapter and also in the "Specification update" document for that particular silicon.

Both 4K & 5K LVs allow the software to "down-size" the caches under software control, allowing eg. benchmarks to be run with different cache-sizes in order to determine the optimal cache size for the final application.

#### 1.2 Dual Bus Modes

One of the main features of the LV chip is that it supports two bus modes: SysAD64 and core bond-out.

The SysAD64 protocol is a industry standard bus protocol which is employed by a wide range of MIPS processors from different vendors. North bridges supporting this bus protocol are also available from several sources.

When the chip is operating in core bond-out mode, the SysAD64 logic is disabled, and the ports on the microprocessor core is instead brought out on the physical LV pins. This allows customers to build a system employing the same bus protocol as they would when designing a real chip using a 4K or 5K core.

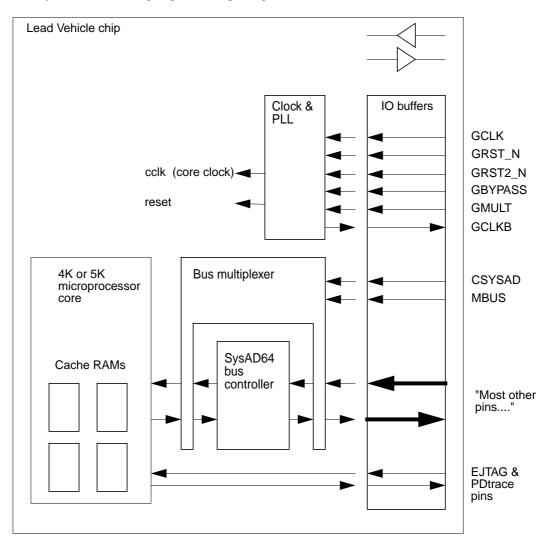

Figure 1 LV Block Diagram

The bus mode is controlled by the CSYSAD input pin which goes to the bus multiplexer. In order to save pins, many pins have two functions depending on the bus mode. This is described in detail in the pinout section.

## 2 Pin Description

This chapter describes the functional pinout of the LV, including a short description of each pin. The AC & DC characteristics and actual pinout on the package are both described in subsequent chapters.

The description is divided into three sections, one covering the shared pins which have identical functions in SysAD64 and bond-out mode, and two tables describing the multiplexed SysAD64 and bond-out mode pins which have different functionality in the two modes. Both the SysAD64 and bond-out mode tables are complete (describing all pins on the device) when seen together with the first table. Note that in the bond-out table, the physical pin name being used for a pin is always the SysAD64 name.

All pin names ending with \_N have negative polarity, all others have positive polarity. A signal ending with "\_N" is asserted or activated when driven low. Some pin names are inherited directly from the corresponding port names on the 4K and 5K cores. These pins do not necessarily follow the above naming convention.

Each pin type is listed as being either "I" (Input), "O" (Output) or "I/O" (Bidirectional pin). There are also a few 3S outputs, these are marked as "O (3S)".

### 2.1 Shared Pins with Identical Function in Both SysAD64 and Bond-out Mode

| Global system level pins |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|--------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin name                 | ne Type Description       |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| GCLK                     | I                         | Master clock input. Normally this clock is used as a reference for the PLL in<br>order to generate the internal core clock, and as such GCLK itself is the bus<br>clock. In PLL bypass mode GCLK is directly used to drive the internal core<br>clock. On the older 4K LVs, the PLL will always generate a 2x core clock. On<br>newer 4K LVs and all 5K LVs, the multiplication factor is configurable (see<br>GMULT pin description).                      |  |  |

| GCLKB                    | 0                         | Outputs the internally generated bus clock which is 1/2, 1/3 or 1/4 of the core clock (for 4K LVs, it will always be 1/2 of the core clock). This relationship between the core clock and the GCLKB output is true regardless of whether the PLL is bypassed or not. This clock should not be used externally on the PCB, since all AC timing parameters are specified with regards to the GCLK input clock. It is only provided for test & debug purposes. |  |  |

| GRST2_N                  | Ι                         | Additional reset for production testing. This pin should always be tied high (deasserted).                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| GBYPASS                  | I                         | Controls PLL bypass mode. Typically the PLL is used when operating the LV bus interface in SysAD64 mode, whereas it should most likely not be used when operating in core bond-out mode.                                                                                                                                                                                                                                                                    |  |  |

|                          |                           | Selects PLL multiplier between externally supplied GCLK and internally generated core clock. It also controls the divider between the internal core clock and the GCLKB output.<br>On the older 4K LVs, the multiplier is fixed to 2x, regardless of these input pins. On newer 4K LVs, and all 4KE/4KS and 5K LVs, the following values                                                                                                                    |  |  |

| GMULT[1:0]               | I                         | on GMULT[1:0] are supported:                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                          |                           | 00: Reserved<br>01: 2x<br>10: 3x<br>11: 4x                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                          |                           | Static configuration pins                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Pin name                 | Pin name Type Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

#### **Table 3 Shared Function Pins**

| CRICEN       | т      | Endianass Configures either big andien or little andien mode                                                                                                                                                                                                                               |

|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBIGEN       | Ι      | Endianess. Configures either big-endian or little-endian mode.                                                                                                                                                                                                                             |

| CTIMER5      | Ι      | If asserted the interrupt signal from the internal timer in the CPU is muxed<br>onto interrupt input 5 internally in the LV. If deasserted, the timer interrupt<br>output signal from the core does not go anywhere in SysAD64 mode (in<br>bond-out mode, it is available on SI_TimerInt). |

| CSYSAD       | Ι      | Selects SysAD64 bus mode (asserted) or core bond-out (deasserted).                                                                                                                                                                                                                         |

|              |        | SysAD64: Selects pipelined writes or R4K style writes on SysAD bus.                                                                                                                                                                                                                        |

| CPIPEWR      | Ι      | If the chip is being operated in core bond-out mode, the value on this pin is ignored. See the SysAD bus protocol description in a later chapter for details.                                                                                                                              |

|              |        | SysAD64: External agent supports 4 word (2 dword) block bursts.                                                                                                                                                                                                                            |

| C4WBLK       | Ι      | If the chip is being operated in core bond-out mode, the value on this pin is ignored. This input put is ignored by the 5K LVs, as they will always perform 4 dword bursts. See the SysAD bus protocol description in a later chapter for details.                                         |

|              |        | EJTAG pins                                                                                                                                                                                                                                                                                 |

| Pin name     | Туре   | Description                                                                                                                                                                                                                                                                                |

| ETCK         | I      | Test clock.                                                                                                                                                                                                                                                                                |

| LICK         |        | External 1k pull-up on PCB must be implemented.                                                                                                                                                                                                                                            |

| ETMS         | I      | Test mode.                                                                                                                                                                                                                                                                                 |

|              |        | External 1k pull-up on PCB must be implemented.                                                                                                                                                                                                                                            |

| ETDI         | I      | Test data input.                                                                                                                                                                                                                                                                           |

|              | -      | External 1k pull-up on PCB must be implemented.                                                                                                                                                                                                                                            |

| ETDO         | O (3S) | Test data output                                                                                                                                                                                                                                                                           |

| ETRST_N      | Ι      | Reset TAP controller.                                                                                                                                                                                                                                                                      |

|              |        | External 1k pull-down on PCB must be implemented.                                                                                                                                                                                                                                          |

| EDINT        | Ι      | External debug interrupt.                                                                                                                                                                                                                                                                  |

|              |        | External 1k pull-up on PCB must be implemented.                                                                                                                                                                                                                                            |

| ERES[11:0]   | 0      | Reserved.                                                                                                                                                                                                                                                                                  |

|              |        | PDtrace pins                                                                                                                                                                                                                                                                               |

| Pin name     | Туре   | Description                                                                                                                                                                                                                                                                                |

| TR_Probe_n   | Ι      | Probe present.                                                                                                                                                                                                                                                                             |

|              |        | External pull-up on PCB must be implemented.                                                                                                                                                                                                                                               |

| TR_TrigIn    | Ι      | Extern trigger input.                                                                                                                                                                                                                                                                      |

| _            |        | External pull-down on PCB must be implemented.                                                                                                                                                                                                                                             |

| TR_TrigOut   | 0      | Extern trigger output.                                                                                                                                                                                                                                                                     |

| TR_Clk       | 0      | Trace clock.                                                                                                                                                                                                                                                                               |

| TR_Data[7:0] | 0      | Trace data.                                                                                                                                                                                                                                                                                |

| TR_DM        | 0      | DebugMode. Is identical to EJ_DebugM, and shares the same physical pin on                                                                                                                                                                                                                  |

## Table 3 Shared Function Pins (Continued)

| Test mode pins (implementor use only) |                                           |                                                                                                                  |  |

|---------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Pin name                              | Pin name         Type         Description |                                                                                                                  |  |

| TSE                                   | Ι                                         | Scan enable. Must be deasserted (tied low).                                                                      |  |

| TSM                                   | Ι                                         | Scan mode. Must be deasserted (tied low).                                                                        |  |

| TSI                                   | Ι                                         | Scan chain data input. Must be deasserted (tied low).                                                            |  |

| TSO                                   | 0                                         | Scan chain data output. Must be left unconnected.                                                                |  |

| TIN[3:0]                              | Ι                                         | Test mode input pins. Must be deasserted (tied low).                                                             |  |

| TIN_N[3:0]                            | Ι                                         | Test mode input pins. Must be deasserted (tied high).                                                            |  |

| TOUT[3:0]                             | 0                                         | Test mode output pins. Must be left unconnected.                                                                 |  |

|                                       |                                           | Test mode pins (MIPS use only)                                                                                   |  |

| Pin name                              | Туре                                      | Description                                                                                                      |  |

| MBUS[1:0]                             | Ι                                         | Bus test modes. Must be deasserted (tied low).                                                                   |  |

|                                       |                                           | Test mode input pins. Must be deasserted (tied low).                                                             |  |

| MINP[2:0]                             | Ι                                         | Since one or more of these pins might become outputs on future devices, a weak pull-down (47k) must be employed. |  |

|                                       |                                           | Test mode input pins. Must be deasserted (tied high).                                                            |  |

| MINP_N[2:0]                           | Ι                                         | Since one or more of these pins might become outputs on future devices, a weak pull-up (47k) must be employed.   |  |

#### **Table 3 Shared Function Pins (Continued)**

All EJTAG pins will typically on the PCB be routed to the EJTAG probe connector. In order to insure stable operation when there is no EJTAG probe attached, the above mentioned pull-ups and -downs must be implemented on the PCB. No pullups/downs are present in the I/O buffers on the LV chip.

Similarly, the above mentioned pull-ups and pull-downs on the PDtrace signals must be implemented on the PCB regardless whether the PDtrace probe connector is present or not. The two PDtrace inputs should never be left floating.

### 2.2 Functional Pin Specification in SysAD64 Mode

#### Table 4 Multiplexed Pin Functions in SysAD64 Mode

| Global system level pins                                                                                                                                                                                                                                                                          |             |                              |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------|--|--|

| Pin name         Type         Description                                                                                                                                                                                                                                                         |             |                              |  |  |

| GRST_N I Reset. The reset pin must be asserted for at least 16 cycles. It may be both asserted and deasserted asynchronously, as the release point is internally synchronized to the core clock. There is no distinction between reset & cold reset, all resets perform a cold reset on the core. |             |                              |  |  |

| SysAD64 bus pins                                                                                                                                                                                                                                                                                  |             |                              |  |  |

|                                                                                                                                                                                                                                                                                                   |             | SysAD64 bus pins             |  |  |

| Pin name                                                                                                                                                                                                                                                                                          | Туре        | SysAD64 bus pins Description |  |  |

| Pin name SSYSAD[63:0]                                                                                                                                                                                                                                                                             | Type<br>I/O |                              |  |  |

| Tabl                 | e 4 Multi | plexed Pin Functions in SysAD64 Mode (Continued)                                                                                                                                                                                                                                                                                                                            |  |

|----------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SSYSADC[7:0]         | I/O       | Check bus (parity for SSYSAD)                                                                                                                                                                                                                                                                                                                                               |  |

| SSYSCMDP             | I/O       | Check bus (parity for SSYSCMD). Currently unused.                                                                                                                                                                                                                                                                                                                           |  |

| SRDRDY_N             | Ι         | Read ready                                                                                                                                                                                                                                                                                                                                                                  |  |

| SWRRDY_N             | Ι         | Write ready                                                                                                                                                                                                                                                                                                                                                                 |  |

| SVALIDIN_N           | Ι         | SSYSADP, SSYSCMDP, SSYSADCP from external agent valid                                                                                                                                                                                                                                                                                                                       |  |

| SVALIDOUT_N          | 0         | SSYSADP, SSYSCMDP, SSYSADCP from CPU valid                                                                                                                                                                                                                                                                                                                                  |  |

| SEXTRQST_N           | Ι         | External agent bus request line. Currently unused.                                                                                                                                                                                                                                                                                                                          |  |

| SRELEASE_N           | 0         | Bus is being released to the external agent                                                                                                                                                                                                                                                                                                                                 |  |

|                      |           | Interrupt pins                                                                                                                                                                                                                                                                                                                                                              |  |

| Pin name             | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                 |  |

| IINT_N[5:0]          | I         | Interrupt inputs. These 6 lines are double synchronized, and then go directly to the 4K/5K core interrupt input ports through an inverter. IINT_N[5] use is determined by the CTIMER5 configuration pin. If CTIMER5 is asserted, IINT_N[5] will be unused.                                                                                                                  |  |

| INMI_N               | I         | NMI (Non-Maskable interrupt) input. Double synchronized, and then<br>connected to the CPU core NMI input through an inverter. The INMI_N input<br>is edge-triggered on the falling edge. The minimum duration of the negative<br>pulse in order to insure detection is 1.5 core clock periods. If the pulse is<br>shorter than 1.5 periods, detection cannot be guaranteed. |  |

|                      |           | Unused pins                                                                                                                                                                                                                                                                                                                                                                 |  |

| Pin name             | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                 |  |

| EB_WData[63:28]      | 0         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| EB_RData[63:0]       | Ι         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| EB_WBErr             | Ι         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| EB_EWBE              | Ι         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| EB_SBlock            | Ι         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| SI_Reset             | Ι         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| SI_MergeMode[1]      | Ι         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| SI_SimpleBE[0]       | Ι         | (Previously this pin was named SI_MergeMode[0])                                                                                                                                                                                                                                                                                                                             |  |

| SI_RP                | 0         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| SI_EXL               | 0         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| EJ_PerRst            | 0         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| EJ_PrRst             | 0         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| EJ_SRstE             | 0         |                                                                                                                                                                                                                                                                                                                                                                             |  |

| EJ_DebugM<br>(TR_DM) | 0         | On LV's supporting PDtrace this pin is named TR_DM and is used as part of<br>the PDtrace pin group (see TR_DM in the previous table).<br>For LV's without PDtrace this pin carries the EJ_DebugM core output<br>(logically identical to TR_DM), which is not really useful in SysAD64 mode.                                                                                 |  |

## Table 4 Multiplexed Pin Functions in SysAD64 Mode (Continued)

| PM_DCacheHit     | 0 |                                                                                                                                                                                                                                                                                        |

|------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PM_DCacheMiss    | 0 |                                                                                                                                                                                                                                                                                        |

| PM_ICacheHit     | 0 |                                                                                                                                                                                                                                                                                        |

| PM_ICacheMiss    | 0 |                                                                                                                                                                                                                                                                                        |

| PM_InstnComplete | 0 |                                                                                                                                                                                                                                                                                        |

| PM_ITLBHit       | 0 | The performance monitoring pins are directly driven by the 4K or 5K core.<br>They are actually also valid in SysAD64 bus modes. It should be noted                                                                                                                                     |

| PM_ITLBMiss      | 0 | however, that they are not synchronized to the bus clock, but rather to the internal core clock, so they might be difficult to sample in PLL mode as the internally generated core clock is not available on a pin. This is why they are placed in the "unused" section of this table. |

| PM_JTLBHit       | 0 |                                                                                                                                                                                                                                                                                        |

| PM_JTLBMiss      | 0 |                                                                                                                                                                                                                                                                                        |

| PM_WTBMerge      | 0 |                                                                                                                                                                                                                                                                                        |

| PM_WTBNoMerge    | 0 |                                                                                                                                                                                                                                                                                        |

| PM_DTLBHit       | 0 |                                                                                                                                                                                                                                                                                        |

| PM_DTLBMiss      | 0 |                                                                                                                                                                                                                                                                                        |

## Table 4 Multiplexed Pin Functions in SysAD64 Mode (Continued)

When operating in SysAD64 mode, all the unused inputs must be tied either high or low to avoid floating inputs. All unused outputs should be left unconnected (or the output value should be ignored).

## 2.3 Functional Pin Specification in Core Bond-out Mode

The table in this section is structured somewhat different that the table in the previous section. The first column gives the pin an alternate name, which is related to the function in core bond-out mode, and the "Type" column specifies the I/O type for the signal (and \*not\* the physical pin type). The "Physical pin name" column shows which physical pin (in most cases a SysAD64 bus pin) is being used for the function. Note that the physical pin type might be a superset of the type specified for the alternate function (typically physically bidirectional pins are being used for either I or O in core bond-out mode).

If the "physical pin name" field is empty, the core bond-out pin has a dedicated pin which is only used in bond-out mode. There are quite a few of these pins, as there are many more active pins in bond-out mode compared to SysAD64 mode, primarily due to the split unidirectional A/D busses.

When the chip is operating with the bus in bond-out mode, all 4K and 5K core signals are directly available on physical pins, with very few exceptions. The signals not available are listed in two tables at the end of this section.

The naming convention with "\_N" for negative polarity signals does not apply for all pin names in this table, as the alternate pin names have been directly taken from the port names on the 4K and 5K cores.

| EC interface pins                                     |   |               |                             |  |  |

|-------------------------------------------------------|---|---------------|-----------------------------|--|--|

| Alternate functionTypePhysical pin<br>nameDescription |   |               |                             |  |  |

| EB_A[35:2]                                            | 0 | SSYSAD[35:2]  | 5K LV: only EB_A[35:3] used |  |  |

| EB_WData[27:0]                                        | 0 | SSYSAD[63:36] |                             |  |  |

#### Table 5 Multiplexed Pin Functions in Core Bond-out Mode

| EJTAG pins         |      |                      |                                               |

|--------------------|------|----------------------|-----------------------------------------------|

| SI_EXL             | 0    |                      |                                               |

| SI_ERL             | 0    | SRELEASE_N           |                                               |

| SI_TimerInt        | 0    | SVALIDOUT_N          |                                               |

| SI_Sleep           | 0    | SSYSCMDP             |                                               |

| SI_RP              | 0    |                      | SI_MergeMode[1] and SI_SimpleBE[0].           |

| SI_SimpleBE[0]     | Ι    |                      | See the section below for more information on |

| SI_MergeMode[1]    | I    |                      |                                               |

| SI_Reset           | Ι    |                      |                                               |

| SI_ColdReset       | I    | GRST_N               |                                               |

| SI_NMI             | Ι    | INMI_N               |                                               |

| SI_Int[5:0]        | Ι    | IINT_N[5:0]          |                                               |

| Alternate function | Туре | Physical pin<br>name | Description                                   |

|                    | *    | System Inte          | erface pins                                   |

| EB_SBlock          | I    |                      |                                               |

| EB_EWBE            | I    |                      | -                                             |

| EB_WWBE            | 0    | SSYSCMD[0]           | -                                             |

| EB_WBErr           | I    | <u> </u>             | -                                             |

| EB_RBErr           | I    | SEXTRQST_N           | -                                             |

| EB_WDRdy           | I    | SVALIDIN_N           | -                                             |

| EB_RdVal           | I    | SWRRDY_N             | -                                             |

| EB_ARdy            | I    | SRDRDY_N             | -                                             |

| <br>EB_BLen[1:0]   | 0    | SSYSCMD[2:1]         | -                                             |

| <br>EB_BLast       | 0    | SSYSCMD[3]           | -                                             |

| <br>EB_BFirst      | 0    | SSYSCMD[4]           | -                                             |

| EB_Burst           | 0    | SSYSCMD[5]           | _                                             |

| <br>EB_Instr       | 0    | SSYSCMD[6]           | -                                             |

| <br>EB_Write       | 0    | SSYSCMD[7]           | -                                             |

| EB_AValid          | 0    | SSYSCMD[8]           |                                               |

| EB_BE[7:0]         | 0    | SSYSADC[7:0]         | 4K LV: only EB_BE[3:0] used                   |

| EB_RData[63:0]     | I    |                      | 4K LV: only EB_RData[31:0] used               |

| EB_WData[63:28]    | 0    |                      | 4K LV: only EB_WData[31:0] used               |

## Table 5 Multiplexed Pin Functions in Core Bond-out Mode (Continued)

| Alternate function   | Туре | Physical pin<br>name | Description                                                                                                                                                                                                                                                                                        |

|----------------------|------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EJ_PerRst            | 0    |                      |                                                                                                                                                                                                                                                                                                    |

| EJ_PrRst             | 0    |                      |                                                                                                                                                                                                                                                                                                    |

| EJ_SRstE             | 0    |                      |                                                                                                                                                                                                                                                                                                    |

| EJ_DebugM<br>(TR_DM) | 0    |                      | On LV's supporting PDtrace this pin is named<br>TR_DM and is used both as part of the PDtrace pin<br>group (see TR_DM in the shared pin table) and as a<br>core port output (EJ_DebugM), usable in the system<br>logic.<br>For LV's without PDtrace this pin carries the<br>EJ_DebugM core output. |

|                      | •    | Performance Mo       | onitoring pins                                                                                                                                                                                                                                                                                     |

| Alternate function   | Туре | Physical pin<br>name | Description                                                                                                                                                                                                                                                                                        |

| PM_DCacheHit         | 0    |                      |                                                                                                                                                                                                                                                                                                    |

| PM_DCacheMiss        | 0    |                      |                                                                                                                                                                                                                                                                                                    |

| PM_ICacheHit         | 0    |                      |                                                                                                                                                                                                                                                                                                    |

| PM_ICacheMiss        | 0    |                      | All these pins are exact copies of ports on the 4K/5K core.                                                                                                                                                                                                                                        |

| PM_InstnComplete     | 0    |                      |                                                                                                                                                                                                                                                                                                    |

| PM_ITLBHit           | 0    |                      | The PM_WTBMerge and PM_WTBNoMerge pins                                                                                                                                                                                                                                                             |

| PM_ITLBMiss          | 0    |                      | are only valid on 4K LVs. On 5K LVs, these pins are reserved for future use.                                                                                                                                                                                                                       |

| PM_JTLBHit           | 0    |                      |                                                                                                                                                                                                                                                                                                    |

| PM_JTLBMiss          | 0    |                      | The PM_DTLBHit and PM_DTLBMiss pins are not valid on 4K LVs based on RTL versions prior to 3.0                                                                                                                                                                                                     |

| PM_WTBMerge          | 0    |                      | (no DTLB in these parts). All other 4K LVs as well<br>as all 4KE, 4KS & 5K LVs drive these pins.                                                                                                                                                                                                   |

| PM_WTBNoMerge        | 0    |                      | ]                                                                                                                                                                                                                                                                                                  |

| PM_DTLBHit           | 0    |                      | ]                                                                                                                                                                                                                                                                                                  |

| PM_DTLBMiss          | 0    |                      | ]                                                                                                                                                                                                                                                                                                  |

|                      |      | Unused               | pins                                                                                                                                                                                                                                                                                               |

| Alternate function   | Туре | Physical pin<br>name | Description                                                                                                                                                                                                                                                                                        |

| N/A                  | 0    | SSYSAD[1:0]          |                                                                                                                                                                                                                                                                                                    |

Table 5 Multiplexed Pin Functions in Core Bond-out Mode (Continued)

When operating in core bond-out mode, all the unused inputs (there are currently none) must be tied either high or low to avoid floating inputs. All unused outputs should be left unconnected (or the output value should be ignored).

## 2.3.1 SI\_MergeMode, SI\_SimpleBE changes

Since the first release of this document and the associated MIPS 4K and 5K cores, some of the cores have been enhanced with two new ports: SI\_SimpleBE[1:0]. At the same time, the meaning of the SI\_MergeMode[1:0] ports has been

changed. For more detailed information on the actual functionality of these ports, please refer to the relevant "Integrator's guide" for the core in question.

For the new cores that have both SI\_MergeMode[1:0] and SI\_SimpleBE[1:0], the LV pinout in core bond-out mode has been slightly changed compared to previous versions of this datasheet. The two balls that previously controlled the two SI\_MergeMode inputs to the core now control one bit of SI\_MergeMode (SI\_MergeMode[1]) and one bit of SI\_SimpleBE (SI\_SimpleBE[0]). This combination has been chosen in order to make the two variants of the LV's as compatible as possible, seen from the outside.

The changes and their effect are described in the two tables below. The first table details which core ports the two LV balls in question are actually routed to inside the various LV types.

The second table describes for each possible value on the two LV balls, how the different LV types will react with respect to write merging and possible byte enable (BE) combinations which can be presented on the EC interface.

| Ball<br>name | Previous pin<br>name | Current pin<br>name | 4K LV use       | 4KE/4KS LV<br>use | 5Kc LV use<br>RTL ver. 2.2 or<br>earlier | 5Kc/f LV use<br>RTL ver. 2.3 or<br>later |

|--------------|----------------------|---------------------|-----------------|-------------------|------------------------------------------|------------------------------------------|

| B10          | SI_MergeMode[1]      | SI_MergeMode[1]     | SI_MergeMode[1] | SI_MergeMode[1]   | Not used                                 | Not used                                 |

| A11          | SI_MergeMode[0]      | SI_SimpleBE[0]      | SI_MergeMode[0] | SI_SimpleBE[0]    | Not used                                 | SI_SimpleBE[0]                           |

## Table 6 Routing of LV balls B10:A11 to SI\_MergeMode and SI\_SimpleBE

### Table 7 Meaning of values on LV balls B10:A11

| Value on<br>B10:A11 | 4K LV<br>SI_MergeMode[1:0]                                       | 4KE/4KS LV<br>SI_MergeMode[1] :<br>SI_SimpleBE[0]             | 5Kc LV<br>RTL ver. 2.2 or earlier                                | 5Kc/f LV<br>RTL ver. 2.3 or later                             |

|---------------------|------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|

| 00                  | No merge<br>Only "natural" MIPS BE<br>combinations               | No merge<br>Only "natural" MIPS BE<br>combinations            |                                                                  | No merge<br>Only "natural" MIPS BE<br>combinations            |

| 01                  | SysAD compliant merge<br>Only SysAD compliant BE<br>combinations | No merge<br>Only naturally aligned<br>B,H,W BE combinations   | Value on inputs ignored.<br>Functionality is always:<br>No merge | No merge<br>Only naturally aligned<br>B,H,W,D BE combinations |

| 10                  | Full merge<br>All BE combinations<br>possible                    | Full merge<br>All BE combinations<br>possible                 | Only "natural" MIPS BE<br>combinations                           | No merge<br>Only "natural" MIPS BE<br>combinations            |

| 11                  | Reserved                                                         | Full merge<br>Only naturally aligned<br>B,H,W BE combinations |                                                                  | No merge<br>Only naturally aligned<br>B,H,W,D BE combinations |

### 2.3.2 Unavailable Core Ports in Bond-out Mode

In core bond-out mode, there are a some ports on the core which are not available as pins on the LV. The two tables below show these pins for both the 4K and 5K LVs (there are a few differences).

| Port name                   | Comment                                                                                                  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------|--|--|

| EJ_ManufID[10:0]            |                                                                                                          |  |  |

| EJ_PartNumber[15:0]         | The values hardcoded on these three core inputs are LV specific and determined by the chip manufacturer. |  |  |

| EJ_Version[3:0]             |                                                                                                          |  |  |

| EJ_DINTsup                  | Hardwired to 1                                                                                           |  |  |